- 您现在的位置:买卖IC网 > Sheet目录478 > MMA8451QT (Freescale Semiconductor)IC ACCELEROMETER 3AXIS 16QFN

�� �

�

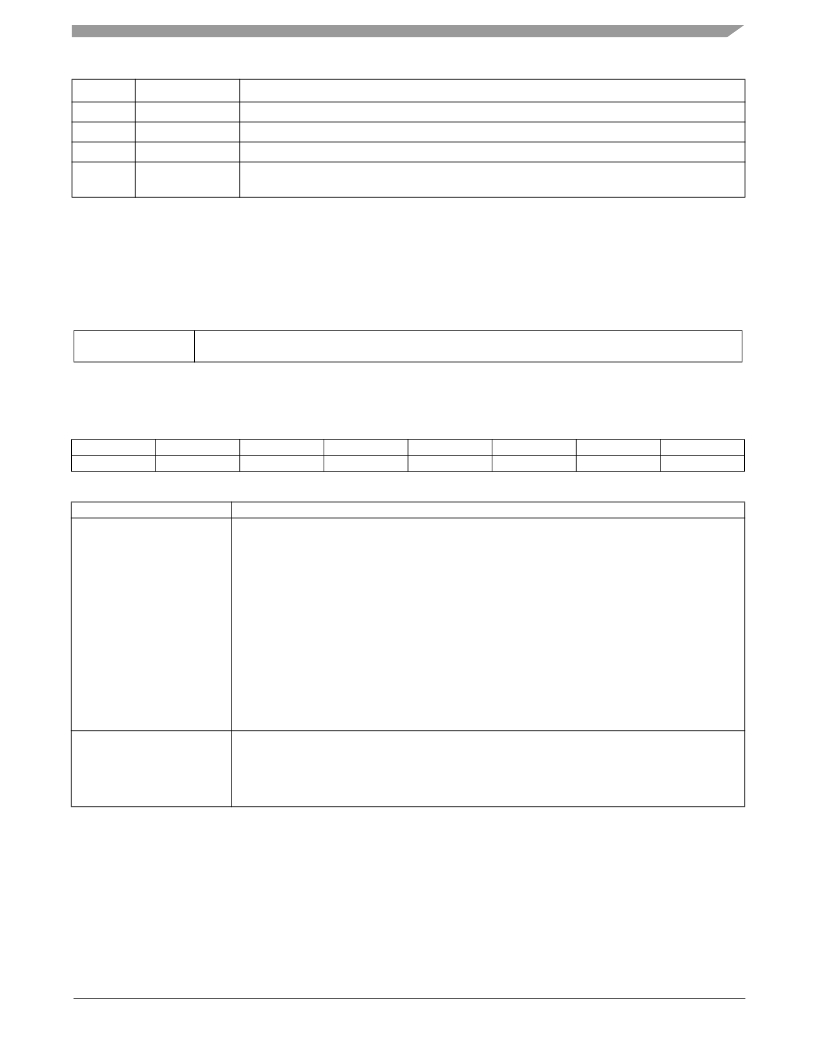

Table� 14.� FIFO� Flag� Event� Description�

�F_OVF�

�0�

�1�

�—�

�—�

�F_WMRK_FLAG�

�—�

�—�

�0�

�1�

�Event� Description�

�No� FIFO� overflow� events� detected.�

�FIFO� event� detected;� FIFO� has� overflowed.�

�No� FIFO� watermark� events� detected.�

�FIFO� Watermark� event� detected.� FIFO� sample� count� is� greater� than� watermark� value.�

�If� F_MODE� =� 11,� Trigger� Event� detected.�

�The� F_OVF� and� F_WMRK_FLAG� flags� remain� asserted� while� the� event� source� is� still� active,� but� the� user� can� clear� the� FIFO�

�interrupt� bit� flag� in� the� interrupt� source� register� (INT_SOURCE)� by� reading� the� F_STATUS� register.� In� this� case,� the� SRC_FIFO�

�bit� in� the� INT_SOURCE� register� will� be� set� again� when� the� next� data� sample� enters� the� FIFO.� Therefore� the� F_OVF� bit� flag� will�

�remain� asserted� while� the� FIFO� has� overflowed� and� the� F_WMRK_FLAG� bit� flag� will� remain� asserted� while� the� F_CNT� value� is�

�equal� to� or� greater� than� then� F_WMRK� value.� If� the� FIFO� overflow� flag� is� cleared� and� if� F_MODE� =� 11� then� the� FIFO� overflow�

�flag� will� remain� 0� before� the� trigger� event� even� if� the� FIFO� is� full� and� overflows.� If� the� FIFO� overflow� flag� is� set� and� if� F_MODE�

�is� =� 11,� the� FIFO� has� stopped� accepting� samples.�

�Table� 15.� FIFO� Sample� Count� Description�

�F_CNT[5:0]�

�FIFO� sample� counter.� Default� value:� 00_0000.�

�(00_0001� to� 10_0000� indicates� 1� to� 32� samples� stored� in� FIFO�

�F_CNT[5:0]� bits� indicate� the� number� of� acceleration� samples� currently� stored� in� the� FIFO� buffer.� Count� 000000� indicates� that� the�

�FIFO� is� empty.�

�0x09:� F_SETUP� FIFO� Setup� Register�

�0x09� F_SETUP:� FIFO� Setup� Register� (Read/Write)�

�Bit� 7�

�F_MODE1�

�Bit� 6�

�F_MODE0�

�Bit� 5�

�F_WMRK5�

�Bit� 4�

�F_WMRK4�

�Bit� 3�

�F_WMRK3�

�Bit� 2�

�F_WMRK2�

�Bit� 1�

�F_WMRK1�

�Bit� 0�

�F_WMRK0�

�Table� 16.� F_SETUP� Description�

�BITS�

�F_MODE[1:0]� (1)(2)�

�F_WMRK[5:0]� (2)�

�Description�

�FIFO� buffer� overflow� mode.� Default� value:� 0.�

�00:� FIFO� is� disabled.�

�01:� FIFO� contains� the� most� recent� samples� when� overflowed� (circular� buffer).� Oldest� sample� is� discarded� to�

�be� replaced� by� new� sample.�

�10:� FIFO� stops� accepting� new� samples� when� overflowed.�

�11:� Trigger� mode.� The� FIFO� will� be� in� a� circular� mode� up� to� the� number� of� samples� in� the� watermark.� The�

�FIFO� will� be� in� a� circular� mode� until� the� trigger� event� occurs� after� that� the� FIFO� will� continue� to� accept� samples�

�for� 32-WMRK� samples� and� then� stop� receiving� further� samples.� This� allows� data� to� be� collected� both� before�

�and� after� the� trigger� event� and� it� is� definable� by� the� watermark� setting.�

�The� FIFO� is� flushed� whenever� the� FIFO� is� disabled,� during� an� automatic� ODR� change� (Auto-WAKE/SLEEP),�

�or� transitioning� from� STANDBY� mode� to� ACTIVE� mode.�

�Disabling� the� FIFO� (F_MODE� =� 00)� resets� the� F_OVF,� F_WMRK_FLAG,� F_CNT� to� zero.�

�A� FIFO� overflow� event� (i.e.,� F_CNT� =� 32)� will� assert� the� F_OVF� flag� and� a� FIFO� sample� count� equal� to� the�

�sample� count� watermark� (i.e.,� F_WMRK)� asserts� the� F_WMRK_FLAG� event� flag.�

�FIFO� Event� Sample� Count� Watermark.� Default� value:� 00_0000.�

�These� bits� set� the� number� of� FIFO� samples� required� to� trigger� a� watermark� interrupt.� A� FIFO� watermark� event�

�flag� is� raised� when� FIFO� sample� count� F_CNT[5:0]� ≥� F_WMRK[5:0]� watermark.�

�Setting� the� F_WMRK[5:0]� to� 00_0000� will� disable� the� FIFO� watermark� event� flag� generation.�

�Also� used� to� set� the� number� of� pre-trigger� samples� in� Trigger� mode.�

�1.� Bit� field� can� be� written� in� ACTIVE� mode.�

�2.� Bit� field� can� be� written� in� STANDBY� mode.�

�The� FIFO� mode� can� be� changed� while� in� the� active� state.� The� mode� must� first� be� disabled� F_MODE� =� 00� then� the� mode� can�

�be� switched� between� Fill� mode,� Circular� mode� and� Trigger� mode.�

�A� FIFO� sample� count� exceeding� the� watermark� event� does� not� stop� the� FIFO� from� accepting� new� data.� The� FIFO� update� rate�

�is� dictated� by� the� selected� system� ODR.� In� ACTIVE� mode� the� ODR� is� set� by� the� DR� bits� in� the� CTRL_REG1� register.� When� Auto-�

�SLEEP� is� active� the� ODR� is� set� by� the� ASLP_RATE� field� in� the� CTRL_REG1� register.�

�When� a� byte� is� read� from� the� FIFO� buffer� the� oldest� sample� data� in� the� FIFO� buffer� is� returned� and� also� deleted� from� the� front�

�of� the� FIFO� buffer,� while� the� FIFO� sample� count� is� decremented� by� one.� It� is� assumed� that� the� host� application� shall� use� the� I� 2� C�

�multi-byte� read� transaction� to� empty� the� FIFO.�

�MMA8451Q�

�Sensors�

�Freescale� Semiconductor,� Inc.�

�23�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MMA8452QR1

IC ACCELER 2G/4G/8G 3AXIS 16QFN

MMA8453QR1

IC ACCELER 2G/4G/8G 3AXIS 16QFN

MMBF0201NLT1

MOSFET N-CH 20V 300MA SOT-23

MMBF170-7

MOSFET N-CH 60V 500MA SOT23-3

MMBF170LT1

MOSFET N-CH 60V 500MA SOT-23

MMBF170

MOSFET N-CH 60V 500MA SOT-23

MMBF2201NT1

MOSFET N-CH 20V 300MA SOT-323

MMBF2202PT1

MOSFET P-CH 20V 300MA SOT-323

相关代理商/技术参数

MMA8452Q

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:3-Axis, 12-bit/8-bit Digital Accelerometer

MMA8452QR1

功能描述:加速计 - 板上安装 LOW G 3-AXIS 12BT EX VLT

RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C

MMA8452QT

功能描述:加速计 - 板上安装 LOW G 3-AXIS 12BT EX VLT

RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C

MMA8453Q

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Xtrinsic MMA8453Q 3-Axis, 10-bit/8-bit Digital Accelerometer

MMA8453QR1

功能描述:加速计 - 板上安装 LOW G 3-AXIS DGTL ACCEL

RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C

MMA8453QT

功能描述:加速计 - 板上安装 LOW G 3-AXIS DGTL ACCEL

RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C

MMA8491Q

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Xtrinsic MMA8491Q 3-Axis Multifunction Digital Accelerometer

MMA8491QR1

功能描述:加速计 - 板上安装 3-Axis Low Voltage Discrete Tilt Sensor

RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C